本文约10,000字,建议收藏阅读

作者 | 北湾南巷

出品 | 芯片技术与工艺

随着计算技术的不断进步,CPU架构的优化和创新成为提升计算性能和降低功耗的关键。高通Nuvia CPU架构作为新一代CPU架构的代表,通过其独特的设计理念和先进的制造工艺,在计算机领域引起了广泛关注。

#01

Nuvia背景与高通收购

1.1 Nuvia的起源和发展

Nuvia成立于2019年,由三位经验丰富的芯片设计师创立:Gerard Williams III、Manu Gulati和John Bruno。这三人此前在业界有着丰富的履历,尤其是在苹果、Google等公司从事核心芯片架构设计。其中,Gerard Williams是苹果的前首席架构师,主导了多个A系列处理器的设计,而Manu Gulati和John Bruno则分别在苹果和Google参与了重要的芯片开发项目。

1.2 Nuvia成立的目标

挑战当前市场上的高性能CPU Nuvia的初衷是为数据中心市场提供新的、高效的CPU解决方案。其首款产品“Phoenix” 设计为一种低功耗高性能的服务器处理器,目标是通过创新的架构设计实现比现有竞争对手更优的性能表现。这一战略引起了业界的广泛关注,尤其是在云计算和数据中心市场对性能和功耗需求不断增加的背景下。

1.3 高通收购Nuvia的动机

2021年,高通宣布以14亿美元收购Nuvia。这一收购具有多重战略意义,主要表现在以下几个方面:

通过收购Nuvia,高通希望打破当前CPU市场的格局,特别是在高性能计算和低功耗设计方面取得更大优势。这一战略举措显示出高通在未来自研技术和市场扩展上的雄心,以及在ARM架构之外谋求更多创新的决心。

1.4 与传统ARM架构的区别

与许多基于ARM的处理器依赖现成设计不同,Nuvia使用的是完全定制的架构,虽然仍遵循ARM指令集,但在核心和非核心部件上进行了大量优化。

这使得Nuvia的设计能够比标准ARM处理器更好地优化特定的数据中心任务,提供显著的性能和功耗管理优势。这种定制化的方式使Nuvia在与现有ARM和x86解决方案的竞争中具有明显的优势。

总结来看,Nuvia的架构设计与传统的CPU设计方式有所不同,通过“从零开始”的定制化ARM架构设计,平衡了高性能与能效的需求,并通过面向特定应用场景的定制优化来满足多样化的市场需求。这种独特的设计理念使其在数据中心市场中拥有明显的竞争力,尤其在云服务提供商注重的性能每瓦指标上表现突出。

#02

Oryon CPU架构

Oryon是Qualcomm新推出的CPU品牌,正是基于Nuvia的设计。这些Oryon核心旨在为Qualcomm的Snapdragon处理器系列提供更强大的计算能力,主要面向Windows-on-Arm笔记本电脑和移动设备。Nuvia的设计虽然最初针对服务器市场,但Qualcomm已计划将其应用于个人计算机等其他市场。

然而,这一过程中也存在法律争议。Arm公司对Qualcomm提起诉讼,声称Qualcomm在未获得许可的情况下使用了Nuvia的设计。这场法律纠纷可能影响Qualcomm使用Arm架构的能力,因为他们仍然依赖于Arm许可的核心和架构。

2.1 Oryon CPU架构介绍

高通披露了Snapdragon X Elite SoC的架构,其中的Oryon CPU核心设计展现了其独特之处。与传统的架构不同,Oryon采用了均匀的核心设计,而非单独针对性能和能效优化的核心。这意味着Oryon核心在性能和能效方面的表现都很突出,而不需要牺牲某一方面的能力。

模块

名称

主要功能

备注

1.CPU部分

Qualcomm Oryon™ CPU

包含12个自定义CPU核心,分为三个簇,每个簇包含4个核心,具有L2缓存共享

高效多核架构,适合多任务处理

CPU簇

CPU Cluster

每个簇包含四个核心,通过L2缓存共享数据,每个簇配有BIU(总线接口单元)

提高数据通信效率,增强多核协同

2.GPU部分

Qualcomm® Adreno™ GPU

负责图形渲染和处理,支持3D图形的高效渲染,优化功耗

适用于游戏和图像密集型应用

3.神经处理单元(NPU)

Qualcomm® Hexagon™ NPU

专为AI和机器学习设计,加速推理与计算操作

用于图像识别和语音处理等AI功能

4.摄像头处理单元

Qualcomm® Spectra ISP™

负责摄像头数据处理,支持高分辨率图像和视频捕获

具备噪声抑制、色彩校正、HDR等高级图像处理功能

5.安全处理单元

Qualcomm® Secure Processing Unit

保护敏感数据,如生物识别信息、加密密钥等,隔离敏感数据以防外部攻击

增强设备的安全性

6.感知集线器

Qualcomm® Sensing Hub

处理低功耗下的传感器数据,适用于手势识别和语音激活等背景传感器应用

提高电池续航,适合持续监测应用

7.内存子系统

Memory SLC + SMMU

包括系统级缓存(SLC)和系统内存管理单元(SMMU),高效管理内存资源和模块间数据共享

提高数据传输效率

8.I/O接口

I/O

负责SoC的输入/输出操作,与外部设备和系统模块通信

提供多样化的设备连接

9.连接性模块

Snapdragon® X65 5G Modem

集成5G调制解调器,支持高速5G连接

确保快速的数据传输

Qualcomm® FastConnect™ 7800

负责Wi-Fi和蓝牙连接,提供低延迟和高速无线通信

适合低延迟应用

10.电源管理模块

PMIC (Power Management Integrated Circuit)

负责整个SoC的电源管理,确保高效稳定的供电

提高系统的能效比

11.音频处理模块

SMB、WCD、WSA

SMB支持快充,WCD为音频编解码器,WSA为扬声器放大器

提高音频质量,增强用户体验

*通过多种核心模块的集成,涵盖了从CPU、GPU到AI处理和传感器管理等各个方面的计算需求。每个模块都经过优化,以提升整体性能,适应各种高性能应用需求,如图像处理、AI计算、游戏、5G通信等。

具体来说,Snapdragon X Elite拥有12个Oryon CPU核心,分为三个集群,每个集群由4个核心组成。所有核心在设计上是平等的,没有专门为能效调整的“效率”集群。因此,在不同负载条件下,所有核心均可提供高性能。此外,两个核心在任何给定SKU中可以达到最高涡轮增压速度,而其余核心则可达到全核心的涡轮增压上限。

每个集群都有独立的相位锁定环(PLL),使得在轻负载时可以将不必要的集群置于休眠状态,从而提升能效并降低功耗。这种设计不仅增强了Snapdragon X Elite的性能,还提升了其在多任务处理和高负载工作下的表现。

2.2 共享L2缓存

高通在其Snapdragon X和Oryon CPU架构中采用了不同于大多数CPU设计的缓存层次结构,具体如下:

模块

描述

详细信息

1. 共享L2缓存的总体设计

12MB 12路共享缓存

每个CPU集群包含一个12MB的共享L2缓存,缓存分为12路组相连(12-way associative),分为12个缓存组以提高命中率。

完全一致性

L2缓存具有完全一致性(Fully coherent),确保所有核心访问相同数据时保持缓存状态一致,防止数据冲突。

MOESI协议

缓存采用MOESI(Modified, Owner, Exclusive, Shared, Invalid)协议管理多核缓存一致性,每个缓存行遵循这五种状态,以便在各核心间进行数据协调。

与核心频率同步

L2缓存的操作频率与核心保持同步,减少频率差异带来的延迟,提高缓存响应速度。

2. L2缓存的数据操作特性

完整的64字节读写操作

L2缓存支持64字节的数据块读写、填充和驱逐操作,适合数据密集型应用的处理需求。

L1缓存包含策略

L2缓存采用L1包含策略,即L2缓存包含所有L1缓存的数据,节约能耗,便于数据备份。L1缓存的数据可以直接从L2读取。

3. 多重低延迟请求优化

优化L1到L2的数据访问

L2缓存针对L1缓存的数据访问进行了优化,确保在L1缓存缺失时能更快找到所需数据。

17周期的平均延迟

L1缓存未命中时访问L2缓存的平均延迟为17个周期,低延迟设计提升系统响应速度。

超过50个进行中的请求

每个核心支持超过50个在飞请求(in-flight requests),允许核心在同一时间内并发发送超过50个请求。

220次内存事务

L2缓存可以同时进行超过220次内存事务,支持高效管理并发请求。

4. 优化的窥视(Snoop)操作

窥视操作

L2缓存优化了窥视操作,用于监控缓存一致性,确保核心间的数据同步。

核心间和集群间的窥视

窥视操作支持核心到核心(Core-to-Core)和集群到集群(Cluster-to-Cluster)的同步,确保多核心系统中的数据一致性。

5. CPU集群结构

核心与缓存布局

每个CPU集群包含四个核心(CORE),核心共享一个位于中央的L2缓存,以便核心之间的快速访问。

总线接口单元(BIU)

位于集群的底部,BIU负责核心与外部模块(如内存和I/O)的数据通信,是L2缓存与外部设备连接的关键部件。

*L2缓存设计显著提高了多核心CPU集群的效率,提供了高容量的共享缓存、低延迟的数据访问和强大的缓存一致性管理

1. 缓存层次结构设计

高通在Snapdragon X和Oryon CPU核心集群上采用了较为扁平的缓存层次结构。这与大多数CPU设计不同,具体而言,每四个核心共享一个L2缓存,而不是每个核心独立配置一个L2缓存。这种设计类似于英特尔在其E核心集群中使用的共享L2缓存方式。Snapdragon X的L2缓存容量为12MB,并且是12路相联的,使得在L1缓存未命中后,访问L2缓存的延迟仅为17个周期。

2. 包容性缓存优势

高通选择了包容性缓存设计,这一选择的优势在于简化了数据驱逐操作。由于L1缓存的数据不需要从L2缓存中移除,这种设计提高了能效。同时,为了确保缓存一致性,高通采用了MOESI协议。此外,L2缓存以全核心频率运行,并支持完整的64字节操作,能够在缓存与CPU核心之间实现数百GB字节的带宽。这种设计不仅服务于直接连接的CPU核心,还优化了集群间的数据访问。

3. 集群配置与性能潜力

值得注意的是,Snapdragon X的四核心集群并不是Oryon CPU集群可以达到的最大配置。高通的工程师表示,设计本身具备支持8核心配置的能力,体现出其作为服务器处理器的潜力。在消费者处理器领域,多个较小的集群设计有助于更细致的电源管理,但也可能导致核心间通信的延迟,影响整体性能。

*Qualcomm Oryon™ CPU:核心数:10或12核;最高主频:3.8GHz多线程;双核心加速频率:最高4.3GHz;总缓存大小:42MB

这一创新设计显著提升了Snapdragon X和Oryon的整体性能与能效,使其在竞争激烈的处理器市场中占据了有利位置。深入分析Oryon CPU核心,可以看到高通为何选择了共享L2缓存的设计:

Oryon核心配备了192KB的L1指令缓存,这一尺寸是Intel Redwood Cove(Meteor Lake)L1 I-Cache的三倍,甚至超过了AMD的Zen 4。这种大容量的L1缓存能够将大量指令更靠近CPU的执行单元,从而提高取指效率。Oryon的取指单元每个周期能够检索多达16条指令,充分利用了这一特性。

宽解码前端

Oryon的解码前端非常宽,单个时钟周期内可以解码多达8条指令,相比之下,Redwood Cove的解码能力为6条,Zen 4则为4条。所有解码器采用对称设计,使得其在不同场景下都能实现全吞吐量,避免了特殊情况的瓶颈。

模块

描述

详细信息

1. 指令缓存(Instruction Cache)

192KB的L1指令缓存

L1指令缓存大小为192KB,采用6路组相连(6-way associative),将缓存划分为6个组,增加缓存命中率。

完全一致性

指令缓存为完全一致性设计(fully coherent),确保在多核心系统中保持数据一致性。

每周期提取16条指令

指令缓存每个时钟周期可提取最多16条指令,加快指令获取速度,提升执行效率。

2. 指令地址转换(Instruction Translation, L1 iTLB)

L1指令转换后备缓冲区(iTLB)

iTLB用于管理取指操作的地址转换,实现虚拟地址到物理地址的映射。

256项8路缓冲

iTLB包含256项条目,采用8路组相连,能够快速映射较大的地址空间,提高地址转换命中率。

支持4KB和64KB的转换粒度

iTLB支持4KB和64KB两种页面大小,适应不同内存页面大小,灵活应对不同的工作负载。

3. 多分支预测表(Multiple Branch Prediction Tables)

单周期分支目标缓冲区(BTB)

分支目标缓冲区在一个周期内预测下一条指令地址,使用程序计数器(PC)分组,提升预测速度。

条件分支预测器

预测下一条分支指令的方向(即是否跳转),保持执行流连续性,减少分支跳转延迟。

间接分支目标预测器

预测间接分支的目标地址,适用于跳转表或函数指针等目标地址不固定的跳转指令。

13周期的分支预测失败延迟

分支预测错误时会导致约13个周期的延迟,分支预测器准确性对于性能尤为重要。

4. 解码(Decode)

每周期解码8条指令

解码单元每周期可解码8条指令,迅速进入执行阶段,解码速度对整体执行效率至关重要。

生成微操作(uOps)

复杂指令在解码时分解成多个微操作(uOps),提高复杂指令的处理效率。

右侧功能单元布局

指令取指单元(IFU)

Instruction Fetch Unit(指令取指单元)从指令缓存中取指,并传递给解码单元。

向量执行单元(VXU)

Vector Execution Unit(向量执行单元)负责执行向量运算,是多媒体、图像处理应用中的关键运算单元。

重命名和退休单元(REU)

Rename and Retire Unit(重命名和退休单元)负责寄存器重命名和指令完成后的资源回收。

整数执行单元(IXU)

Integer Execution Unit(整数执行单元)专门用于执行整数运算的单元。

内存管理单元(MMU)

Memory Management Unit(内存管理单元)负责地址转换、内存保护和缓存管理等内存相关操作。

*分支预测和指令解码单元,并在执行单元方面分工明确,能够满足多任务和复杂计算的需求,提高了处理器的性能和多线程处理能力。

微操作和分支预测

在指令被解码后,它们被转化为微操作(uOps)供CPU核心进一步处理。尽管每条ARM指令理论上可以解码为多达7个uOps,但高通表示,实际情况下,Arm v8指令与微操作的比例通常接近1:1。分支预测也是提升CPU性能的关键因素,Oryon设计了直接、条件和间接等多种预测器。直接预测器的响应速度为一个周期,但错误预测会导致13个周期的延迟。

L1转换旁视缓冲区和总结

此外,Oryon的L1转换旁视缓冲区(TLB)用于虚拟到物理内存地址的映射,具有256个条目的容量,支持4K和64KB的页面。这一设计有助于提高内存访问效率。总体来看,Oryon的设计通过优化缓存和解码机制,展示了高通在CPU架构创新上的雄心,预计将成为其未来产品(包括移动SoC和汽车领域应用)的核心支柱。

2.3 后端执行转换

高通Oryon执行后端的转换时,有几个关键点值得深入探讨:

功能模块

详细信息

寄存器重命名(Register Rename)

独立的重命名池

整数执行单元(IXU)和向量执行单元(VXU)各有独立的重命名池,避免资源冲突,提升执行效率。

整数寄存器池

包含400多个整数寄存器,为整数操作提供充足的寄存器资源。

向量寄存器池

包含400多个向量寄存器,满足向量和SIMD操作需求。

保留站(Reservation Stations)

整数执行单元(IXU)

具有6条宽64位的流水线,每条流水线的保留队列为20个条目,可同时处理多个整数操作请求,并通过队列减少资源争用。

向量执行单元(VXU)

拥有4条宽128位的流水线,每条流水线的保留队列为48个条目,支持复杂的向量运算,适合多媒体和科学计算。

加载/存储单元(LSU)

具有4条宽128位的流水线,每条流水线的保留队列为16个条目,负责数据的加载和存储操作。

整数执行流水线

(Integer Execution Pipes)

每周期支持6次ALU操作

整数执行单元每周期可执行多达6次算术逻辑单元(ALU)操作,显著提升整数运算的并行度。

每周期支持2次分支操作

每个时钟周期内可以处理多达2次分支指令,减少分支预测误差对流水线的影响。

每周期支持2次乘法/乘加操作

支持每周期2次乘法或乘加操作,适合需要高效数学运算的应用(如机器学习、图像处理等)。

向量执行流水线(Vector Execution Pipeline for FP and NEON SIMD)

每条流水线宽度达128位

VXU的每条流水线可以处理128位的数据,以支持单指令多数据(SIMD)操作,加速浮点运算和多媒体应用。

每周期支持4次浮点和整数运算

每周期可执行4次浮点32位加法、乘法、乘加(F32-ADD/MUL/MLA)或整数32位的ALU和乘加操作(INT32-ALU/MLA),提升浮点和整数运算的吞吐量。

支持多种数据类型

VXU支持INT8、INT16等整数类型及FP16、FP32、FP64等浮点类型,兼容广泛的数据处理需求。

指令退休

(Instruction Retirement)

按顺序退休

指令退休按程序执行顺序进行,每周期最多退休8条微操作(uOps),确保程序执行正确性。

重排序缓冲区

配备650多个微操作的重排序缓冲区(Re-Order Buffer),用于保存即将退休的指令,确保指令顺序性和数据一致性。

*展示了处理器不同执行单元的寄存器重命名、保留站、整数和向量流水线以及指令退休的详细配置和功能,有助于理解系统的高效执行机制。

重排序缓冲区(ROB)设计

Oryon配备了超过650个条目的重排序缓冲区,这一设计旨在通过乱序执行显著提升指令并行性和整体性能。高通通过采用大规模的ROB打破了传统设计理念,挑战了关于大型ROB可能导致收益递减的观点,从而在CPU架构设计中引入了创新。

指令退役能力

Oryon的解码器每周期可以输入8条指令,并输出8个微操作(uOps)。尽管理论上每条指令可以生成多个微操作,但在实际应用中,解码器的输出通常与指令退役速率保持一致,这样确保了高效的指令处理,降低了潜在的处理延迟。

寄存器重命名池

Oryon还具有一个庞大的寄存器重命名池,提供超过400个整数运算寄存器及额外的400个用于向量单元,这种设计为高效的并行处理提供了强有力的支持,进一步提升了CPU的执行能力。

执行管道设计

Oryon的执行管道包括6个整数管道、4个浮点数/向量管道和4个加载/存储管道。虽然高通未披露每个管道的详细功能,但所有整数管道均能执行基本的算术逻辑单元(ALU)操作,其中2个支持分支处理,2个可以执行复杂的乘累加(MLA)指令。大多数整数操作的延迟为一个周期,这使得其能够实现高效的即时执行。

关于浮点数和向量处理,Oryon的每个向量管道配备了NEON单元,支持经典的128位NEON指令。虽然这一限制使得其处理的向量宽度低于当前PC CPU(如AVX2的256位),但在所有浮点管道配置NEON单元在一定程度上弥补了这一不足,尤其是在AI时代,这些管道支持多种常见数据类型,包括INT8。

综上所述,Oryon的设计思路在于通过创新的硬件架构实现高效的执行性能,充分利用丰富的缓冲区和寄存器资源,展现了高通在CPU设计领域的技术优势和进步。

2.4 数据加载存储

关于高通Oryon的数据加载/存储单元,以下是几个关键点:

功能模块

详细信息

数据缓存

(Data Cache for Load-Store)

96KB的L1缓存

配备完全一致(fully coherent)的96KB 6路组相连L1缓存,支持64字节(B)的一致性粒度,提供快速的数据访问并确保多核系统中的数据一致性。

多端口设计

L1缓存具有多端口和精细分片的设计,支持不同大小的访问请求,提高并发访问效率。

数据转换

(Data Translation for Load-Store, L1 dTLB)

地址转换管理

加载/存储单元使用L1数据转换旁路缓冲区(L1 dTLB)管理地址转换,对虚拟内存管理至关重要。

224条目、7路组相连缓冲区

dTLB包含224个条目,采用7路组相连结构,能够缓存地址转换结果,减少重复转换的开销。

支持4KB和64KB的转换粒度

多粒度转换支持不同大小的内存页面,提供更高灵活性,适应不同内存访问场景。

加载/存储执行流水线

(Load-Store Execution Pipes)

每周期支持4次加载/存储操作

流水线每周期可执行最多4次任意组合的加载和存储操作,显著提高数据处理吞吐量。

支持从存储到加载的转发

实现数据刚存入存储单元时即可被加载单元使用的转发,减少数据依赖等待,提升效率。

加载和存储队列

包含192条目加载队列和56条目存储队列,管理未完成的加载和存储操作,确保执行流畅。

与大容量L2缓存紧密集成

加载/存储单元与大容量L2缓存集成,支持64字节填充,减少内存访问延迟,提高数据访问效率。

预取技术(Prefetching)

多种高级预取技术

使用多种高级预取技术,提前加载数据至缓存,减少加载数据时的等待时间。

预取算法

包括相邻行、步幅、指针、数组等多种数据模式,能够预测并预加载常见访问模式的数据。

多级预取支持

支持L1数据缓存、L2缓存和数据转换缓冲区的预取,在多个缓存级别优化数据访问。

*展示了处理器不同执行单元的寄存器重命名、保留站、整数和向量流水线以及指令退休的详细配置和功能,有助于理解系统的高效执行机制。

灵活的加载/存储单元

Oryon核心的加载/存储单元设计具有高度的灵活性。四个执行管道能够在每个周期内执行任意组合的加载和存储操作,支持高效的并行处理。加载队列的深度可达到192个条目,而存储队列的深度则为26个条目,确保了在复杂的运算中能够快速访问和存储数据。

L1数据缓存的性能

Oryon的L1数据缓存相当庞大,具有96KB的大小,采用6路关联缓存架构。这一设计使得Oryon在数据访问时表现出色,尤其是与Intel的Redwood Cove相比,Oryon的缓存容量几乎是其两倍,虽然Intel即将推出的Lion Cove可能会改变这一状况。缓存被细致划分以支持不同的访问模式,这进一步提升了数据处理的效率。

内存预取技术

高通在内存预取器的设计上也颇具特色,声称这一单元对整体性能的贡献极大。尽管具体的预取机制没有详细披露,但其核心功能在于准确预测并预取数据,这在现代处理器的高时钟速度下,尤其重要。预取算法能够覆盖多种数据访问模式,利用历史访问记录来预测未来的数据需求,从而显著减少访问延迟。

总体来看,Oryon的加载/存储单元不仅提供了灵活的操作能力和强大的缓存支持,还通过高效的内存预取技术提升了数据处理性能。这些特性标志着高通在CPU设计领域的重要进步,特别是在高效能计算和现代应用需求日益增长的背景下。

2.5 内存管理单元(MMU)功能

功能模块

详细信息

内存管理单元(Memory Management Unit, MMU)

MMU负责内存地址转换和虚拟内存管理,确保处理器高效访问和管理内存。

支持4KB和64KB的转换粒度

MMU支持4KB和64KB的内存页大小转换,适应不同应用场景需求。

多页大小支持

每个粒度下支持多种不同大小的内存页面,提供更高的灵活性。

虚拟化和双级转换(2-stage Translation)

支持虚拟化和两级地址转换,以高效管理虚拟机内存。

嵌套虚拟化

支持嵌套虚拟化,允许客体虚拟机(Guest VM)上运行子虚拟机(Guest-Hypervisor),增强多层虚拟化灵活性。

L1指令TLB和L1数据TLB

VA-to-PA地址转换

L1指令和数据TLB支持虚拟地址(VA)到物理地址(PA)的转换,满足所有类型的数据流量需求。

单周期访问

L1 TLB支持单周期访问,处理器可以在一个时钟周期内完成地址转换,降低内存访问延迟。

L2-TLB统一缓存

>8K条目,8路组相连结构

L2 TLB包含超过8K条目,并采用8路组相连结构,高效存储和访问大量地址转换结果。

适用于大内存占用应用

专为大内存需求应用设计,确保在高内存访问需求下具备高效地址转换能力。

页表缓存(Table-Walk Caches)

缓存中间节点描述符

页表缓存存储多级页表结构中各级的描述符,减少对主存的访问,提升地址转换速度。

硬件页表遍历器(Hardware Table Walker)

每个核心支持多个并发的页表遍历

硬件页表遍历器支持每个核心多个并发页表遍历请求,确保高并发下高效处理地址转换请求。

*列出MMU的各项功能,包括其在地址转换、虚拟化支持、多级页表遍历以及缓存优化方面的特性。

设计与功能

Oryon的MMU设计相对简单,但具备现代MMU的多项功能,包括支持嵌套虚拟化,使得一个客户虚拟机能够托管其他客户虚拟化管理程序。这种设计增强了虚拟机的支持能力。

硬件表遍历器

Oryon MMU中包含一个硬件表遍历器,负责在DRAM中查找数据。当缓存行不在L1或L2缓存中时,它可以同时进行多达16个表遍历。这一功能为每个核心提供支持,因此在完整的Snapdragon X芯片上,最多可实现192个并行表遍历操作。

这种设计在多任务和高负载情况下表现出色,能够保持系统性能的稳定性。Oryon的MMU特性使其在移动设备和高性能计算环境中具有显著优势,从而增强了Qualcomm在市场上的竞争力。Oryon MMU的这些特性使得它在现代计算需求中能够高效运作,并为高负载场景下的性能提升提供了保障。

2.6 内存子系统

组件

属性

值

系统级缓存(SLC)

容量

6MB

延迟时间

26到29纳秒(ns)

带宽

每个方向135 GB/s

动态随机存取存储器(DRAM)

类型

LPDDR5x

规格

8448 MT/s,8个通道,16位宽度

带宽

135 GB/s

最大内存容量

64 GB

延迟时间

102到104纳秒(ns)

在图中可以看到,CPU集群由多个核心组成,每个核心都有自己的二级缓存(L2 Cache)。这些核心通过总线接口单元(BIU)与系统级缓存(SLC)进行交互。同时,它们还通过fabric与DRAM子系统相连,从而实现数据的读写操作。整个系统的设计旨在优化性能和效率,确保数据能够在不同的层次之间高效地流动。

L3缓存配置

在Oryon芯片的共享内存子系统中,最后的缓存级别为共享的L3缓存。尽管芯片的L1和L2缓存已经相当庞大,Oryon的L3缓存却仅为6MB,这只是其支持的36MB L2缓存的一小部分。这个设计决策与高通在其Arm移动SoC中通常采用较小的L3缓存风格相一致。

缓存策略

高通选择了一种相对较小的victim缓存作为在访问系统内存之前的最后一站。这与传统x86 CPU的设计有所不同,后者通常会配置更大的L3缓存。然而,Oryon的L3缓存具有极快的访问速度,延迟仅为26-29纳秒,能够与DRAM(135GB/秒)提供相同的带宽,用于在L2缓存和DRAM之间传递数据。

内存支持

Snapdragon X芯片配备了128位内存总线,支持LPDDR5X-8448,最大内存带宽达到135GB/秒。在当前的LPDDR5X容量下,Snapdragon X最多支持64GB的RAM,未来若高通推出更高密度的LPDDR5X芯片,128GB的验证也在预期之中。

内存配置与延迟

与一些专注于移动设备的芯片不同,Snapdragon X并未使用封装内内存,LPDDR5X芯片将直接安装在设备的主板上,由设备供应商自行选择内存配置。高通表示,使用LPDDR5X-8448内存时,DRAM的延迟在102-104纳秒之间,这在性能上是一个重要的考量。

这些设计特征展示了Oryon在缓存和内存管理方面的策略,充分考虑了高效性和性能之间的平衡,使其在现代计算环境中具有竞争力。

2.7 CPU的安全性

安全措施类别

具体措施

描述

控制流完整性措施(Control Flow Integrity Measures)

指针认证(Pointer Authentication)

在执行时验证指针完整性,防止代码注入等攻击。

分支目标ID(Branch Target ID)

确保分支指令的目标地址是预期的,防止恶意跳转到错误的位置。

内置硬件侧信道缓解措施(Side-Channel Mitigations built into Hardware)

针对已知的攻击向量

对抗各种已知的安全漏洞和攻击方式。

熔毁(Meltdown)、幽灵(Spectre)等

防护熔毁和幽灵等著名安全漏洞。

使用内部块密码进行微架构混淆

通过加密技术隐藏处理器内部的敏感信息,增加攻击难度。

每个集群专用的随机数发生器(Dedicated Random Number Generator per Cluster)

独立的随机数发生器

每个处理器的核心群集都有一个独立的随机数发生器,提高安全性,对加密操作至关重要。

最先进的安全架构(State of the Art Security Architectures)

信任区(Trustzone)

隔离区域,运行受保护的代码和数据,增强安全性。

密码学扩展(Cryptographic Extensions)

提供额外的加密功能支持。

指针认证、分支目标ID

强调指针认证和分支目标ID的重要性。

推测屏障和RCTX指令

推测屏障限制处理器对未授权数据的访问,RCTX是新的安全指令集。

随机数生成

强调随机数生成在安全中的作用。

不受最近发布的攻击影响(Not susceptible to recently published attacks (circa 2017-2024))

PACMAN、直线猜测、奥古里、GoFetch

表明CPU设计对这些特定的攻击类型具有抵抗力。

安全功能支持

高通在其现代芯片中集成了多种先进的安全功能,包括Arm TrustZone、每个计算集群配备的随机数生成器,以及指针认证等安全加固措施。这些功能旨在保护数据和系统的完整性,确保在复杂的计算环境中维持高水平的安全性。

侧信道攻击的防护

高通特别指出,Oryon CPU 针对已知的侧信道攻击(如Spectre)实施了有效的缓解措施。值得注意的是,Spectre本身并不是一个硬件漏洞,而是推测执行所固有的一个副作用,这使得完全防御这一攻击变得极为复杂,通常的最佳策略是通过自我隔离来保护敏感操作。

硬件混淆技术

尽管应对侧信道攻击具有挑战性,高通相信通过在硬件设计中应用多种混淆技术,可以有效抵御这类攻击。这些混淆技术旨在增加攻击者获取敏感信息的难度,从而提升芯片的安全性和可靠性。

2.8 较高的性能

高通宣称Snapdragon X在每核心基础上,其性能高于竞争对手AMD和英特尔的架构,并且效率也更高。

如图所示,比较了四种不同的处理器:Snapdragon X Elite、AMD Ryzen 9 7940HS、Intel Core Ultra 9 155H和Intel Core Ultra 9 185H。Qualcomm Oryon™ CPU在性能和能效方面具有竞争优势,尤其是在低功耗区间,能够提供更高的性能。这对于移动设备和需要高效能处理的应用程序来说是一个重要的优势。

参考:

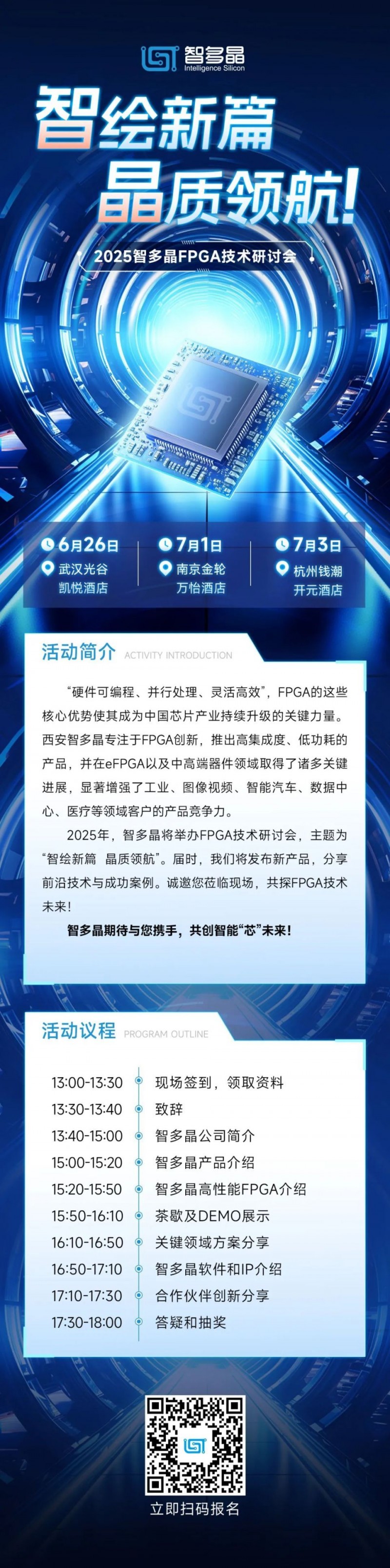

注:自6月26日起,本土FPGA头部企业智多晶将在武汉、南京、杭州举行巡回技术研讨会,分享新产品、新应用、新技术。与会嘉宾都将获赠一份精美的伴手礼,会上也将有价值千元的奖品抽出。欢迎各位从业者踊跃报名,在会上分享和交流~